# Gateware and Software for ALS-U Instrumentation

L. M. Russo<sup>†</sup>, A. Amodio, M. J. Chin, W. E. Norum, K. Penney, G. J. Portmann, J. M. Weber

Accelerator Technologies Group, ATG Lawrence Berkeley National Laboratory, LBNL, Berkeley, California, USA <sup>†</sup>lucasrusso@lbl.gov

### Introduction

The Advanced Light Source Upgrade (ALS-U) is a diffraction-limited light source upgrade project under development at the Lawrence Berkeley National Laboratory. The Instrumentation team is responsible for developing hardware, gateware, embedded software and control system integration for diagnostics projects, including Beam Position Monitor (BPM), Fast Orbit Feedback (FOFB), High Speed Digitizer (HSD), Beam Current Monitor (BCM), as well as Fast Machine Protection System (FMPS) and Timing. This work describes the gateware and software approach to these projects, its challenges, tests and integration plans for the novel accumulation and storage rings and transfer lines.

#### **Beam Position Monitor (BPM)**

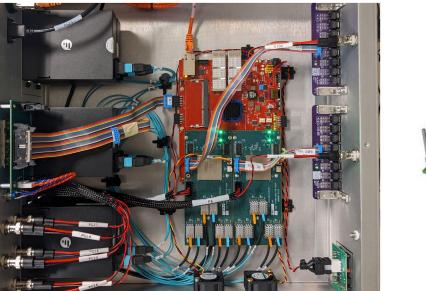

## Timing Stream 2 EVF Chassis

#### Hardware

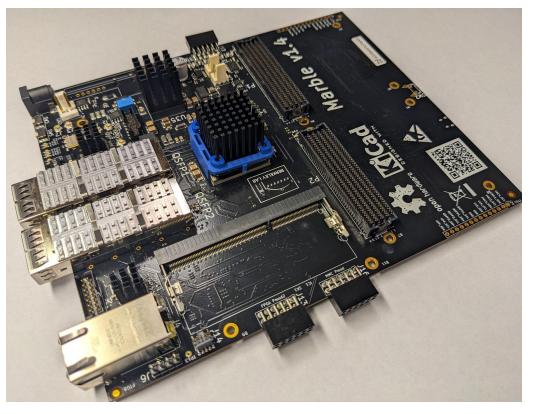

#### **Kintex7 Marble**

https://github.com/berkeleylab/Marble

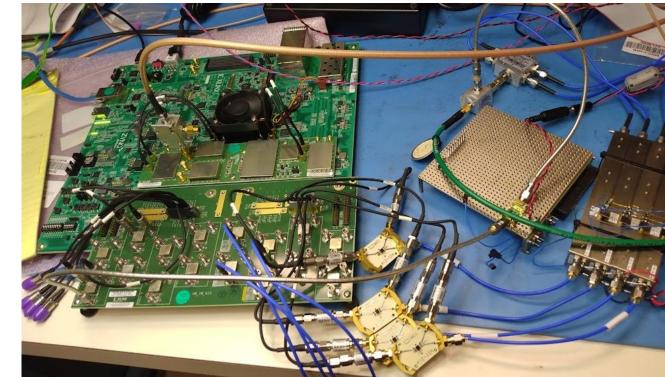

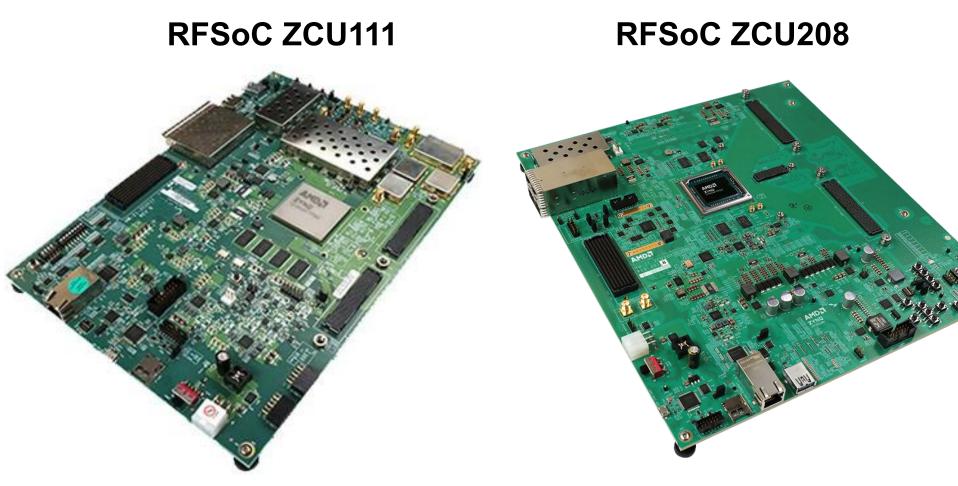

RFSoC BPM bench setup, 5GSPS, 14-bit ADC (left: Xilinx ZCU208 platform, right: 4 AFE modules)

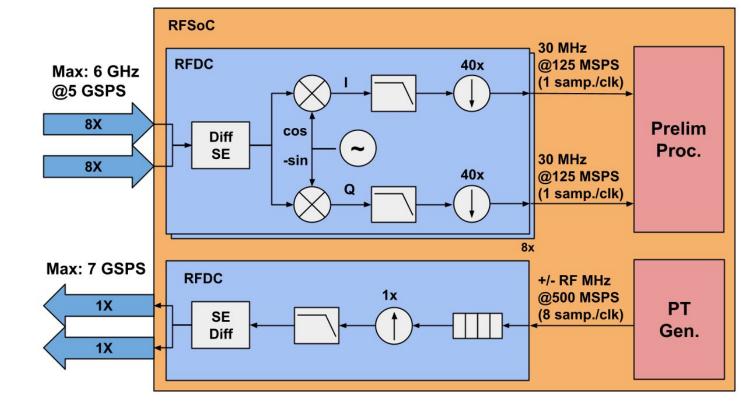

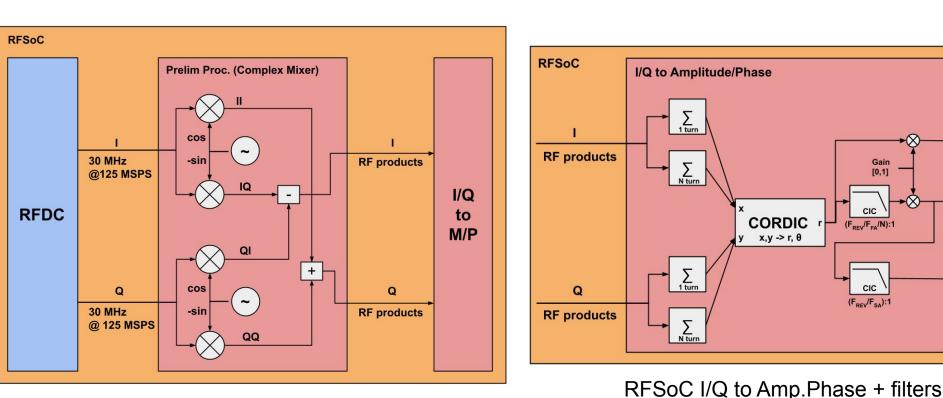

Open source gateware and embedded software consisting of: 2-stage DDC for amplitude demodulation; flexible acquisition engine to external SDRAM, continuous pilot tone calibration, rich status monitoring.

RFSoC BPM first DDC stage and PT generation

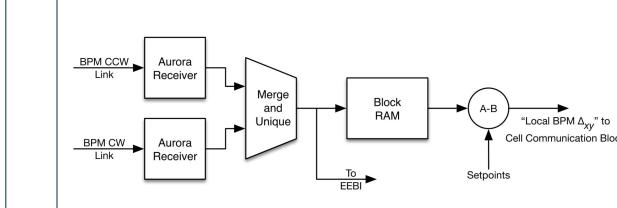

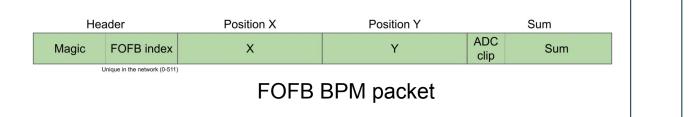

Fast Orbit Feedback (FOFB)

PS Setpoints

1 Gb/s

PSC1

PSC3

Ethernet fiber links

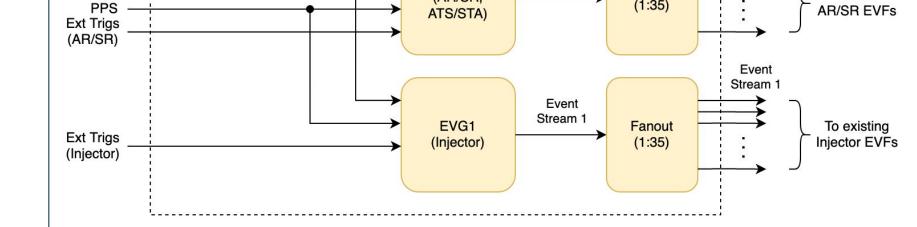

Timing system architecture

Event Stream 2

**EVG** Chassis

FMC EVRIO

FMC EVIO

ALS-U Timing EVG

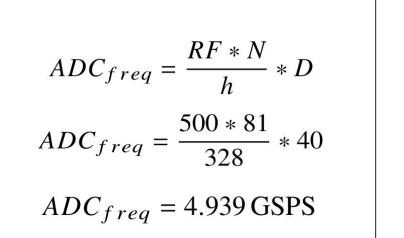

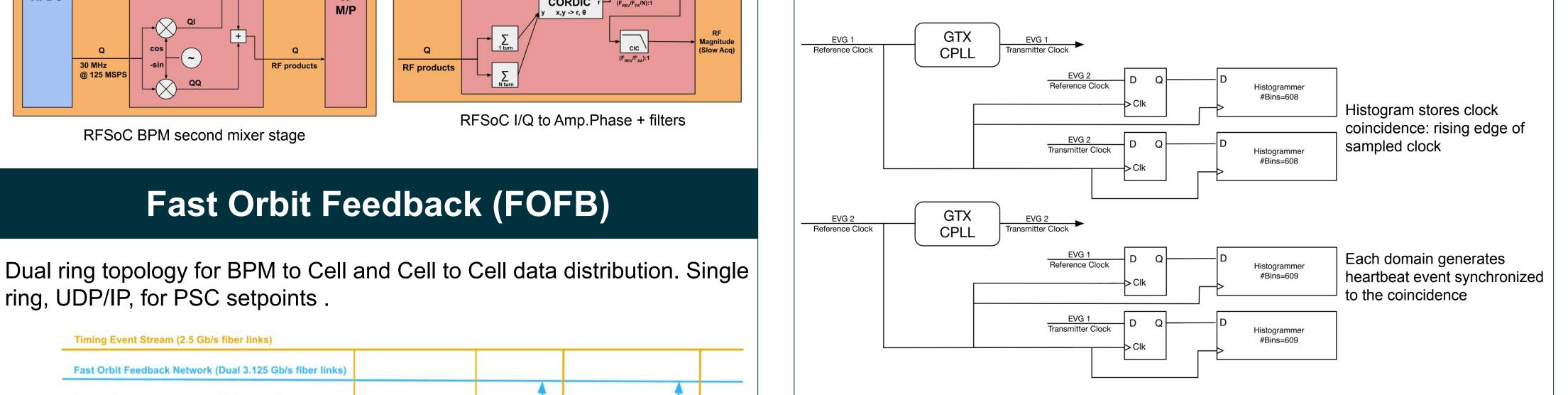

ALS-U timing system needs to support injection across 2 different RF domains  $RF_{ini}$  and  $RF_{sr}$  with  $RF_{ini} = 608/609*RF_{sr}$ .

https://www.xilinx.com/products/boards-and-kits/zc u111.html

https://www.xilinx.com/products/boards-and-kits/z cu208.html

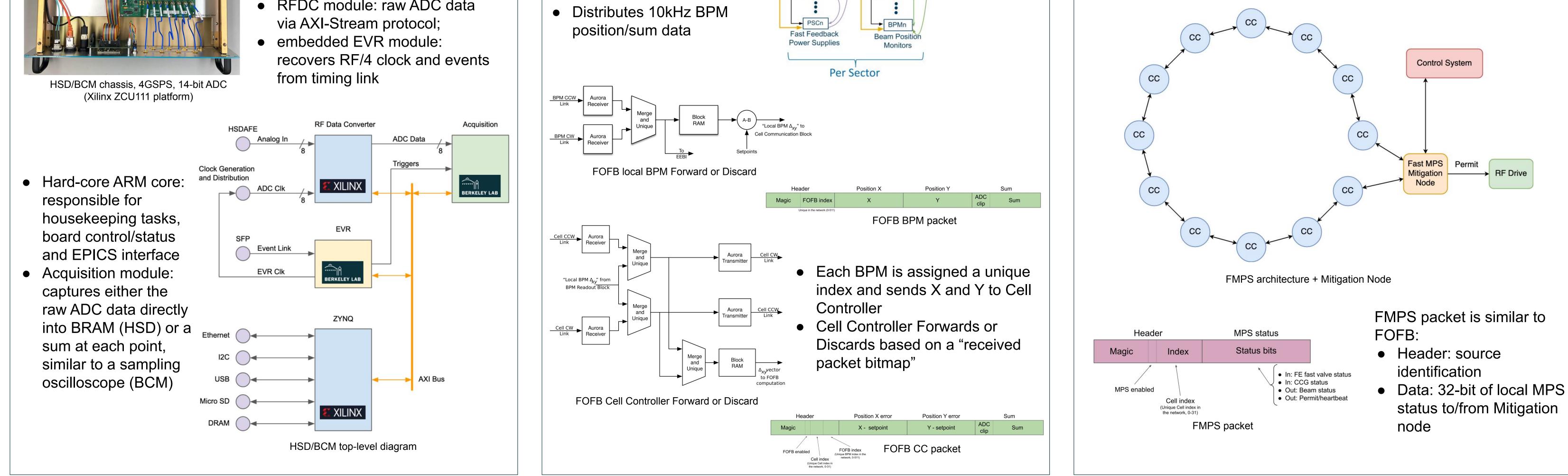

## High Speed Digitizer (HSD/BCM)

HSD uses a ZCU111 demoboard + an in-house developed AFE to acquire signals at 4GSPS, 14-bit, DC. Timing system synchronized: • ADC sampling clock

- Triggers

- Timestamp

Gateware components:

- RFDC module: raw ADC data via AXI-Stream protocol;

- from timing link

Cell

Controller

BPM1

BPM2

BPM3

BPM4

BPM5

...

**BPM** Positions Dual 3.125 Gb/s

fiber links

Cell

Controller

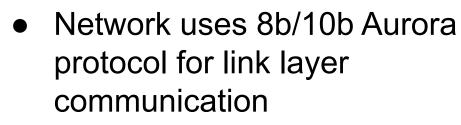

### **Fast Machine Protection System (FMPS)**

FMPS shares the FOFB deterministic network and uses the Cell Controller nodes to inject new FMPS packets into the network. Mitigation node acts like a 13<sup>th</sup> node and uses position data + status to act on RF.

RFSoC BPM second mixer stage

ring, UDP/IP, for PSC setpoints.

Timing Event Stream (2.5 Gb/s fiber links)

Control System Network – EPICS (Ethernet)

Fast Orbit Feedback Network (Dual 3.125 Gb/s fiber links