# O LEAPS INNOVATION

## TOWARDS DEFINING A SYNCHRONIZATION STANDARD BETWEEN BEAMLINE COMPONENTS AND SYNCHROTRON ACCELERATORS

Under the umbrella of LEAPS-INNOV project\*, the Task 3 of Work Package 5 aims to define a standard for synchronization in the beamline sample environment. Their main partners (ALBA, DESY, DLS, ESRF and SOLEIL) have already reached a common vision of synchronization requirements. Trying to approach the utopic vision of a transparent synchronization integration of beamline parts with minimal effort and the reality of a experimental setup highly dynamic and diverse. The challenges of this work package come to fruition in 2 parts: Hardware synchronization device and a synchronization protocol.

## Phases of the project

- Collate Existing Solutions and Future Requirements of Facilities for Beamline Synchronization (Done)

- Definition of the demonstrator Experiment for Beamline Synchronization (Done)

- Definition of a Standard Protocol for Synchronization between Beamline Components (On going)

- Installation of the Synchronisation Protocol and Demonstrator Experiment at several facilities (March'25)

#### Hardware

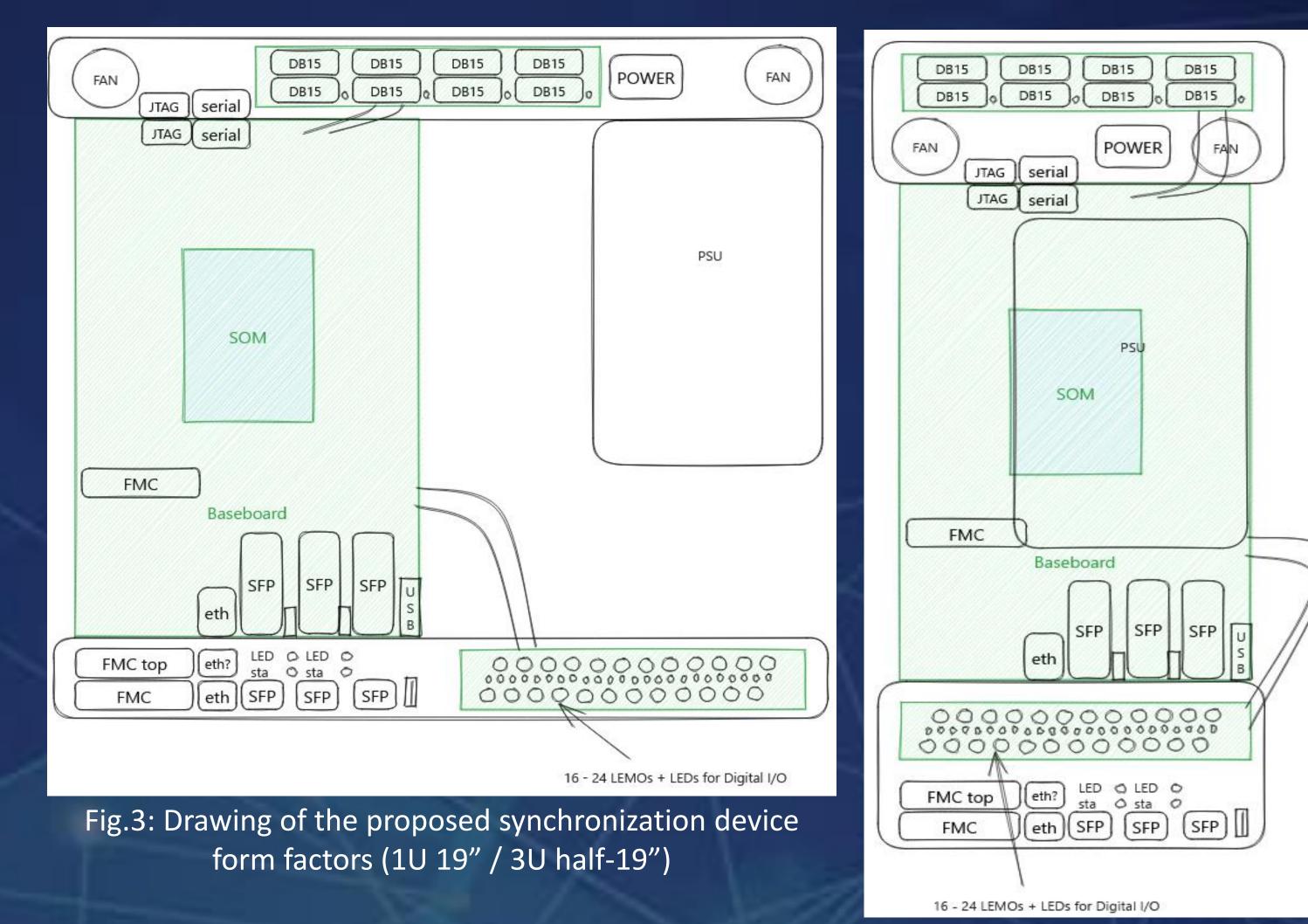

Many facilities have a real need of a synchronization equipment in the sample environment. As consequence, some of them have enrolled in the specification of it, coming to an agreement.

| /  | Name                          | Input/<br>Output | Signal Type /<br>Impedance                              | Form<br>factor             | Minimal<br>Quantity    | Optimal<br>Quantity | Bandwidth<br>(Hz)  | Jitter (s)           |

|----|-------------------------------|------------------|---------------------------------------------------------|----------------------------|------------------------|---------------------|--------------------|----------------------|

|    | Interface<br>#1 -<br>DIFFIO   | 1/0              | Diff / 120Ω<br>(RS422)                                  | DB15                       | 4                      | 8                   | 50 MHz             | 1us                  |

| ł  | Interface<br>#2 -<br>DIO      | 1/0              | Selectable LVTTL<br>(TTL comp) / 50Ω<br>/ High-Z        | Lemo 00                    | 10                     | 20                  | 200 MHz            | 8ns                  |

| t  | Interface<br>#3 -<br>DO       | 0                | 50Ω                                                     | Lemo 00                    | 2                      | 4                   | 200 MHz            | 30ps (fine<br>delay) |

|    | Interface<br>#4 -<br>EXP      | IO               | Vita 57.1                                               | FMC LPC                    | 1 (LPC)                | 2                   | FMC<br>standard    | NA                   |

|    | Interface<br>#5 -<br>OPT      | IO               | Fiber optics                                            | SFP+                       | 2                      | 4                   | 12.5Gbps           | NA                   |

| 18 | Interface<br>#6 -<br>ETHERCAT | I/O              | Ethernet                                                | RJ45                       | 1                      | 1                   | 10GBps             | NA                   |

|    | Interface<br>#7 -<br>MNGMNT   | IO               | RS232, JTAG, USB,<br>ETH etc.                           | DB9, JTAG,<br>USB,<br>RJ45 | 2 (RS232,<br>ETH)      | 4 (All)             | Standard           | NA                   |

|    | Interface<br>#8 -<br>Al       | I                | Analog Input<br>Range selectable<br>[+/-1V, 0-5V], Hi-Z | BNC                        | 0 (Optional<br>on FMC) | 8                   | 1MHz ADC,<br>16bit | NA                   |

|    | Interface<br>#9 -<br>AO       | 0                | Analog Output<br>Range [+/-10V],<br>1kOhm               | BNC                        | 0 (Optional<br>on FMC) | 4                   | 1MHz DAC,<br>16bit | NA                   |

|    | Interface<br>#10 -<br>CLKIN   | I                | RF Clock Input                                          | SMA                        | 0 (Optional<br>on FMC) | 1                   | 500MHz             | 20ps                 |

|    | Interface<br>#11 -<br>CLKOUT  | 0                | RF Clock Output                                         | SMA                        | 0 (Optional<br>on FMC) | 1                   | 500MHz             | 20ps                 |

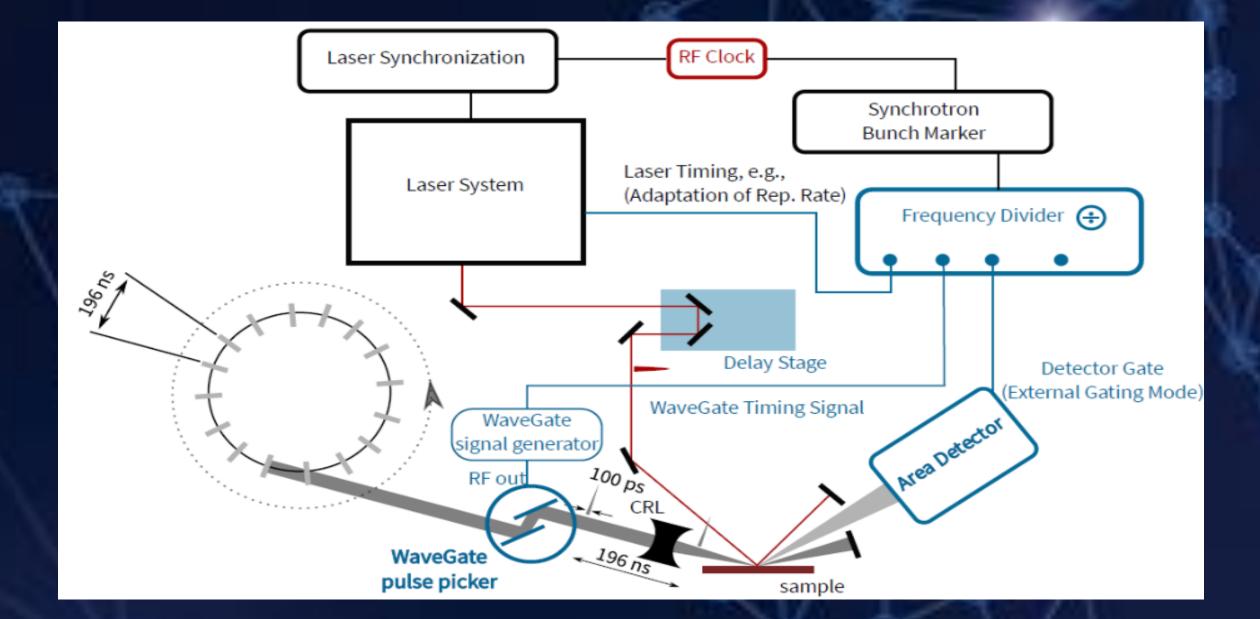

Fig.1: Demonstrator experiment

### Synchronization Protocol

The project aims for the definition of a synchronization protocol to allow the description of the synchronization needs in all the ranges of time precisions. Moreover, it should be user-friendly for the experimenters, maybe with the use of a graphical tool, but also it must be simple to be interpreted by the SCADA systems and lately translated to the devices involved in the synchronization.

#### Table.1: Final specification proposal for HW I/O interface

#### <u>Number of signals</u>

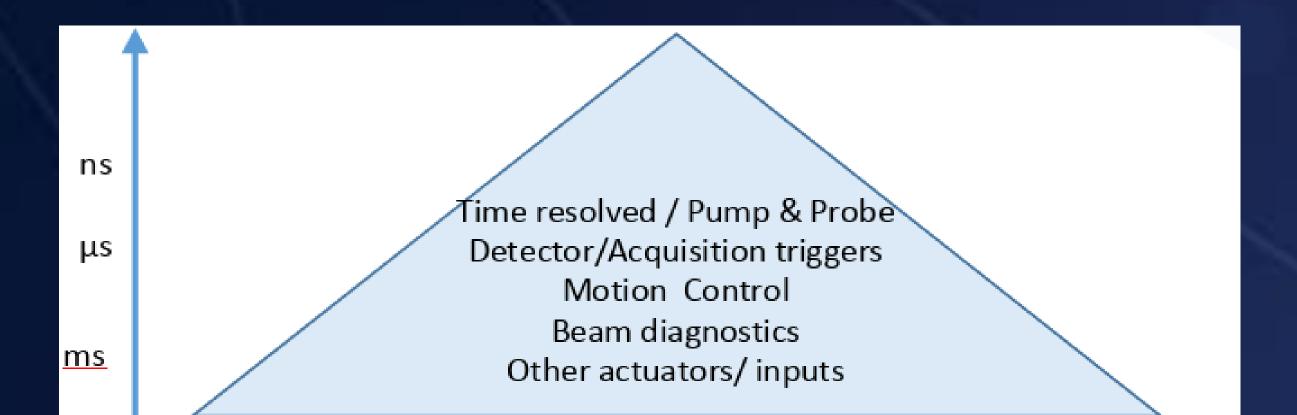

Fig.2: Relation between the time precision requirements and its quantity

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement no. 101004728.

\* https://leaps-initiative.eu/

ZB

**Zentrum Berlin**

European

XFEL