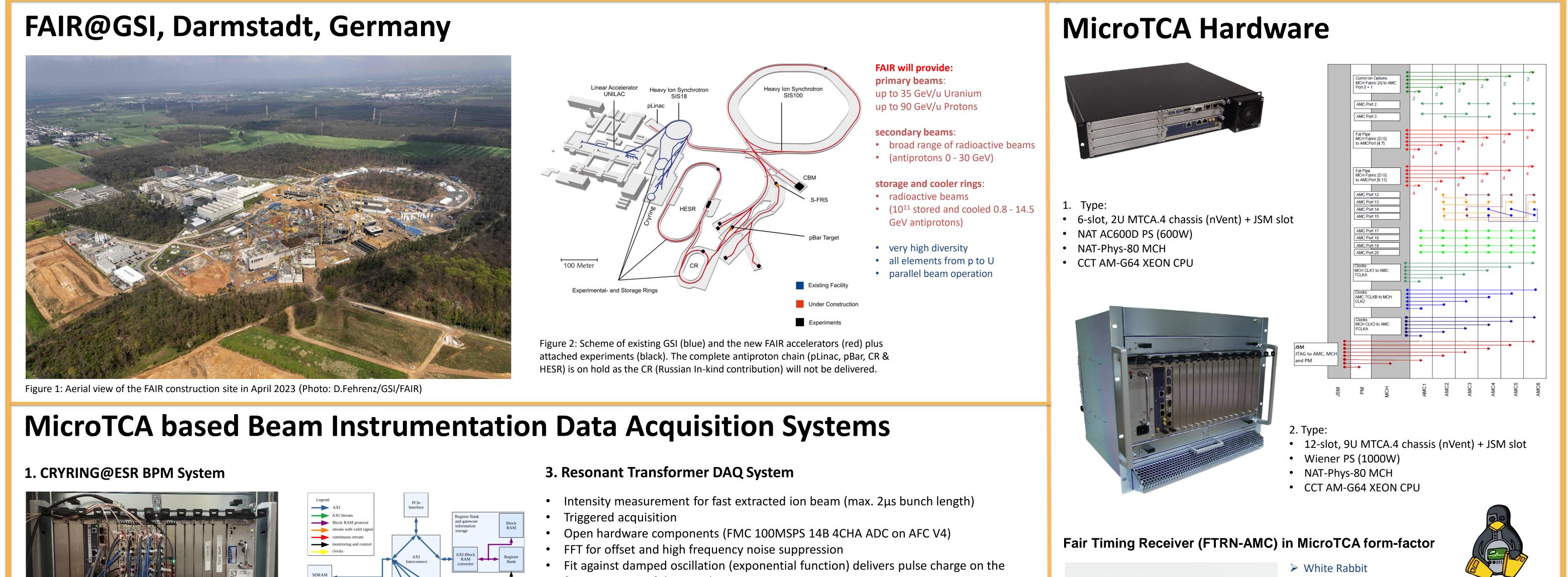

# STATUS OF THE MICROTCA BASED BEAM INSTRUMENTATION

MO4A007

# DAQ SYSTEMS AT GSI AND FAIR

T. Hoffmann, H. Bräuning, R. Geißler, T. Milosic GSI Helmholtzzentrum für Schwerionenforschung, Darmstadt, Germany

# Abstract

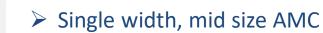

As the first FAIR accelerator buildings are soon to be completed, MicroTCA-based data acquisition (DAQ) systems for FAIR beam instrumentation are ready for use. By using commercial off-the-shelf (COTS) components as well as open hardware with in-house expertise in FPGA programming, there are now DAQ solutions for almost all major detector systems in MicroTCA in operation at the existing GSI accelerators. Applications span a wide range of detector systems and hardware, often taking advantage of the high channel density and data transmission bandwidth available with MicroTCA. All DAQ systems are synchronised and triggered using a comprehensive White Rabbit based timing system. This allows correlation of the data from the distributed acquisition systems on a nanosecond scale.

We present some examples of our DAQ implemented in MicroTCA covering the range of beam current, tune, position and profile measurements. While the latter uses GigE cameras in combination with scintillating screens, the other applications are based on ADCs with different sampling frequencies between 125MSa/s up to 2.5GSa/s or latching scalers with up to 10MHz latching frequency.

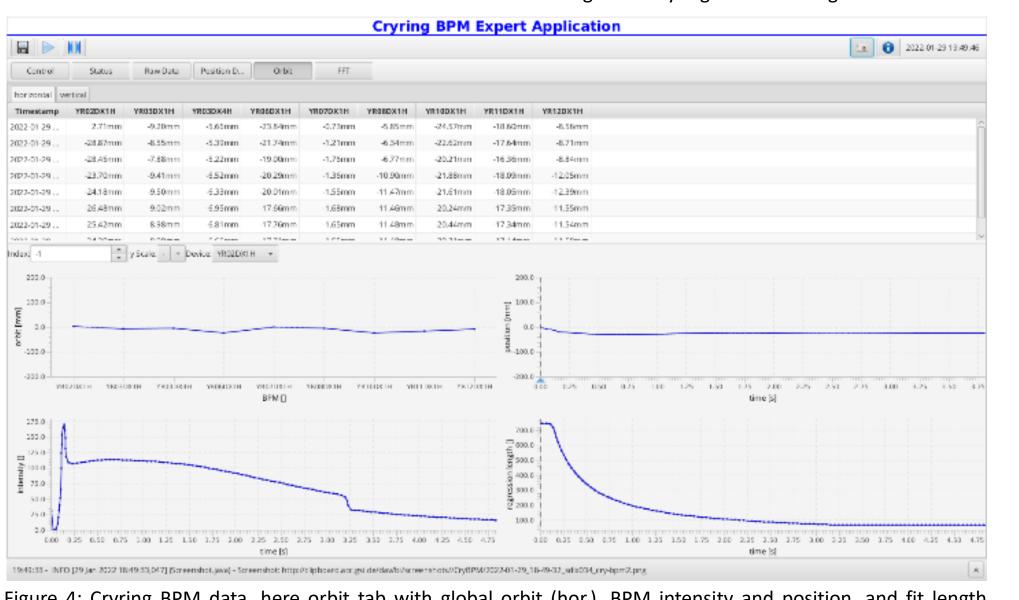

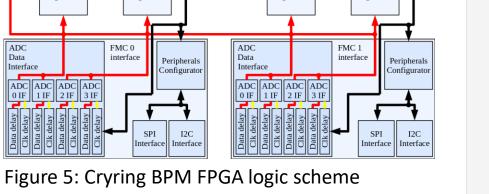

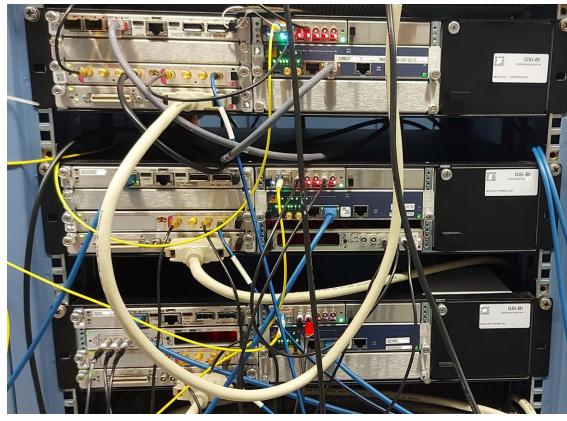

Figure 3: CRYRING@ESR Beam Position Monitoring system using AFC V3.1 FMC carrier modules with 250MSPS/4Ch/16 Bit ADC FMCs.

- Open Hardware / FMC technology

- Gate pulse from FTRN via M-LVDS

- first maximum of the signal.

- > Open hardware (see ohwr.org/project/tr-amc/

- Bi-directional I/Os

- Clock and time / time-stamping

- Generate digital pulses and clock signals

- Generate specified interrupts at given times

- FPGA based data evaluation:

- ➢ Raw ADC data

- Position data

- Averaged position data

Averaging Algorithm

врм

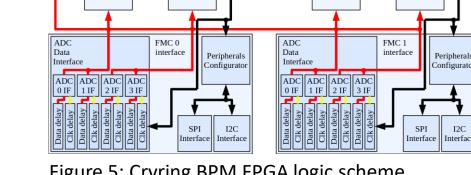

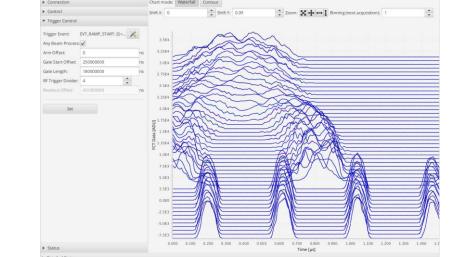

Figure 4: Cryring BPM data, here orbit tab with global orbit (hor.), BPM intensity and position, and fit length (regression)

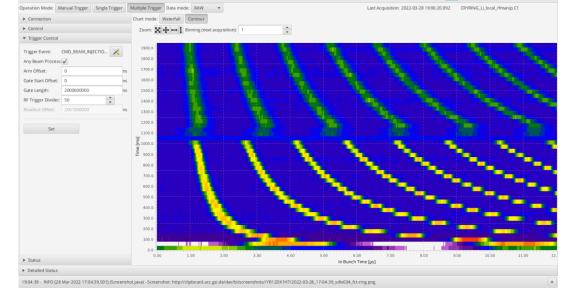

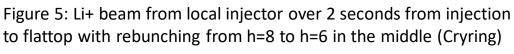

### 2. Fast Current Transformer System

- Intensity and bunch structure measurement of fast extracted ion beam (max. 2µs bunch length)

- GSI-Rings (SIS18, ESR, Cryring) and transfer lines (HEBT), later also at FAIR SIS100, HEBT

- Triggered by RF master (bunch synchronous)

- Data reduction by rate divider in FPGA logic (FMC 5-channel Digital I/O)

## Bunch dynamics during RF manipulations:

| FCT: YR12DX1HT                               |                                    |

|----------------------------------------------|------------------------------------|

| 🔚 🗐 🕑 📄 🔢 Selector: CRYRING_LL_local_rfm 👻 🌾 | 🔝 📃 German 👻 🚯 2022-03-28 19:06:26 |

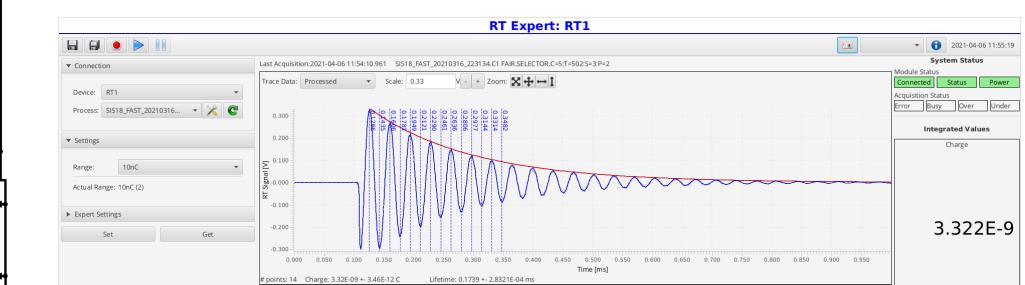

Figure 8: : Typical resonant intensity signal using a resonant transformer with fast extracted ion beam

## 4. Profile Video Imaging for Scintillating Screens

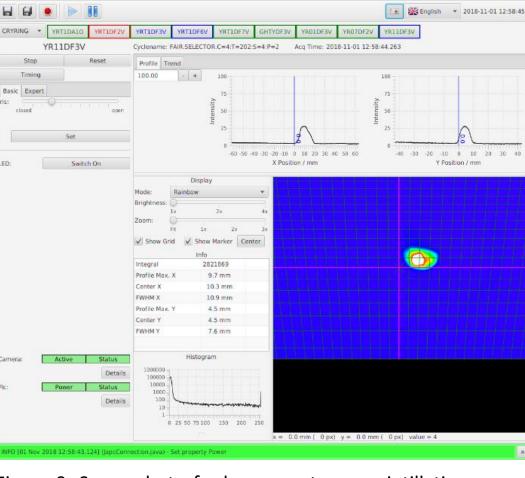

Figure 9: Screenshot of a beam spot on a scintillating screen with data evaluation like projections, FWHM, centre of mass etc.

GigE cameras:

➢ Ueye UI-5240SE

framegrabber

• FTRN-AMC

MegaRAD3 (Thermo Fisher)

radhard analog with Pleora

Vadatech AMC217 Switch

triggered or free running

Figure 10: Scintillating screen DAQ system

## **5. Particle Counter Expert System**

• High performance multi-channel DAQ for spill micro-structure analysis with plastic scintillators at slow extracted ion beam.

#### Custom functionality via LM32 cores

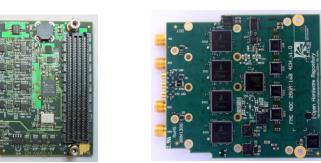

#### Advanced FMC Carrier (AFC)

- > Open hardware (see https://ohwr.org/project/afc)

- Developed by Warsaw University of Technology (WUT)

- and LNLS, Brazil

- Xilinx Artix-7 200T FFG1156 FPGA

- Dual slot HPC FMC carrier w/wo RTM on demand

#### **FMC and AMC Modules**

OHWR FMC ADC 100N

14B 4CHA (Image

Source: ohwr.org)

OHWR FMC ADC 250M 16B

4CHA (Image Source:

ohwr.org)

Struck FMC 2500M 14B

2CHA DC on SIS8160 FMC

Carrier (Image Source:

struck.de)

IOXOS FMC ADC\_3117 5M 16B 20CHA (Image Source: ioxos.ch)

**OHWR FMC 5-channel Digital** I/O (Image Source: ohwr.org)

Struck SIS8800 MTCA.4 Struck SIS8980 MTCA.4 32CHA multiscaler 16CHA Leading Edge (Image Source: struck.de) Discriminator (Image Source: struck.de)

Struck SIS8864 MTCA 64CHA digital I/O board (Image Source: struck.de)

Vadatech AMC217 8CHA LAN Switch (Image Source: vadatech.com

### OUTLOOK

New intensity-, transmission-, and beam-loss monitoring system at the UNILAC

Figure 7: FCT DAQ systems for HEBT, ESR and SIS18

FCT: GS01DT1F

🔛 🕘 🕨 📗 selector: SIST8\_FAST\_HHD\_RRF... 🔹 🔀 💽

Figure 6: SIS18 40Ar18+ beam, 300MeV/u, bunch merging h=4 to h=1

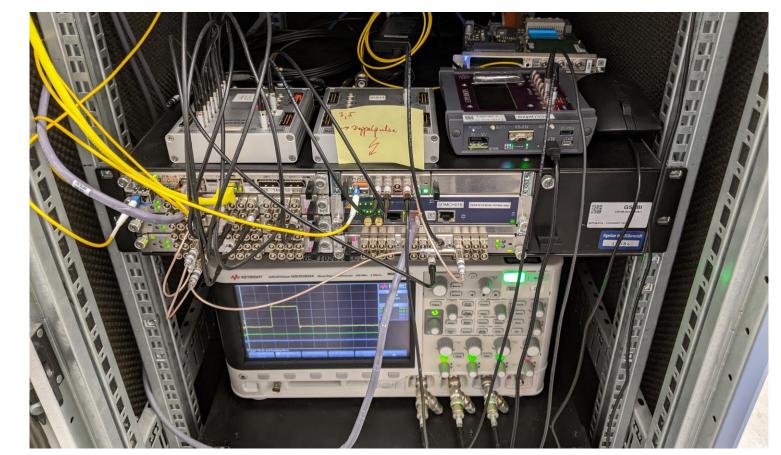

Modular FCT DAQ concept with:

- FTRN-AMC (timing receiver)

- SIS8160/SFMC01 ADC

- SIS8864 I/O

- Rate divider (AFC+5CH DIO)

SIS8800 Multiscaler with SIS8980 LE Discriminator µRTM Continuous readout, untriggered

- Readout in multi-channel scaler mode (MCS) into DMA

- Complete record of all timing messages in parallel

- High efficiency and performance achieved by pipelined concept 10MHz@128channels

- Next: Spill duty factor evaluation, FFT, Spectrogram

Figure 11: Setup of LASSIE Expert prototype system using four SIS8800 scalers in parallel

- Sampling of 64 AC transformers in parallel

- 50 Hz Unilac repetition rate

- >40 timing domains

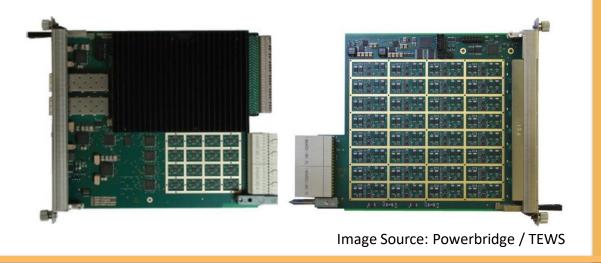

- Digitizer: 5 x TEWS TAMC532 32-channel ADCs at 50MSPS/16Bit plis µRTM, reduced to 10MSPS

- Digitisation of analog transformer signal and its correlated frame pulse

#### Digitizer:

- TEWS TAMC532 + RTM

- > 32 Ch. via RTM with 8xRJ45

- > 75/50 MSPS 12/14 Bit

- triggered readout at 50Hz

- (Unilac)

#### ACKNOWLEDGEMENTS

The authors would like to thank the colleagues from CERN BE-CCS for many years of inspiration in software and hardware concepts. In particular, we would like to acknowledge the introduction of the CERN Open Hardware License. Furthermore, we would like to thank DESY for the valuable workshops, tutorials and support around MicroTCA. Big thanks also go to the many supporting industry partners such as Struck (SIS), Powerbridge, Tews, Emcomo, NAT, Wiener and Schroff. Finally we would like to thank Piotr Miedzik for major contributions in settling FPGA and OHL technology within the BEA-DAT team at GSI.

Facility for Antiproton and Ion Research in Europe GmbH | GSI Helmholtzzentrum für Schwerionenforschung GmbH